¶

Les microcontrôleurs de la famille AVR d'Atmel¶

Caractéristiques générales¶

- Technologie CMOS haute vitesse : rapidité + faible consommation

- Architecture RISC et Harvard

- Puissance en Mips = fréquence de l'horloge

- Alimentation entre 1,8 et 5,5V

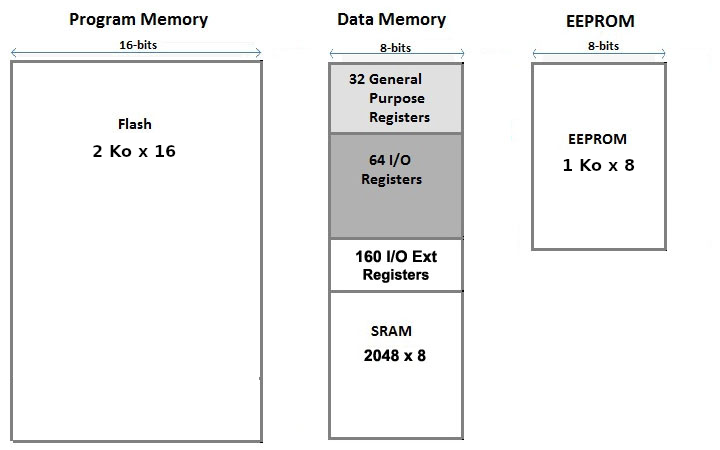

- 3 mémoires indépendantes :

- Mémoire flash intégrée (10000 cycles écriture)

- Mémoire EEPROM pour le stockage de données semi-permanentes

- (100000 cycles écriture)

- Mémoire SRAM rapide

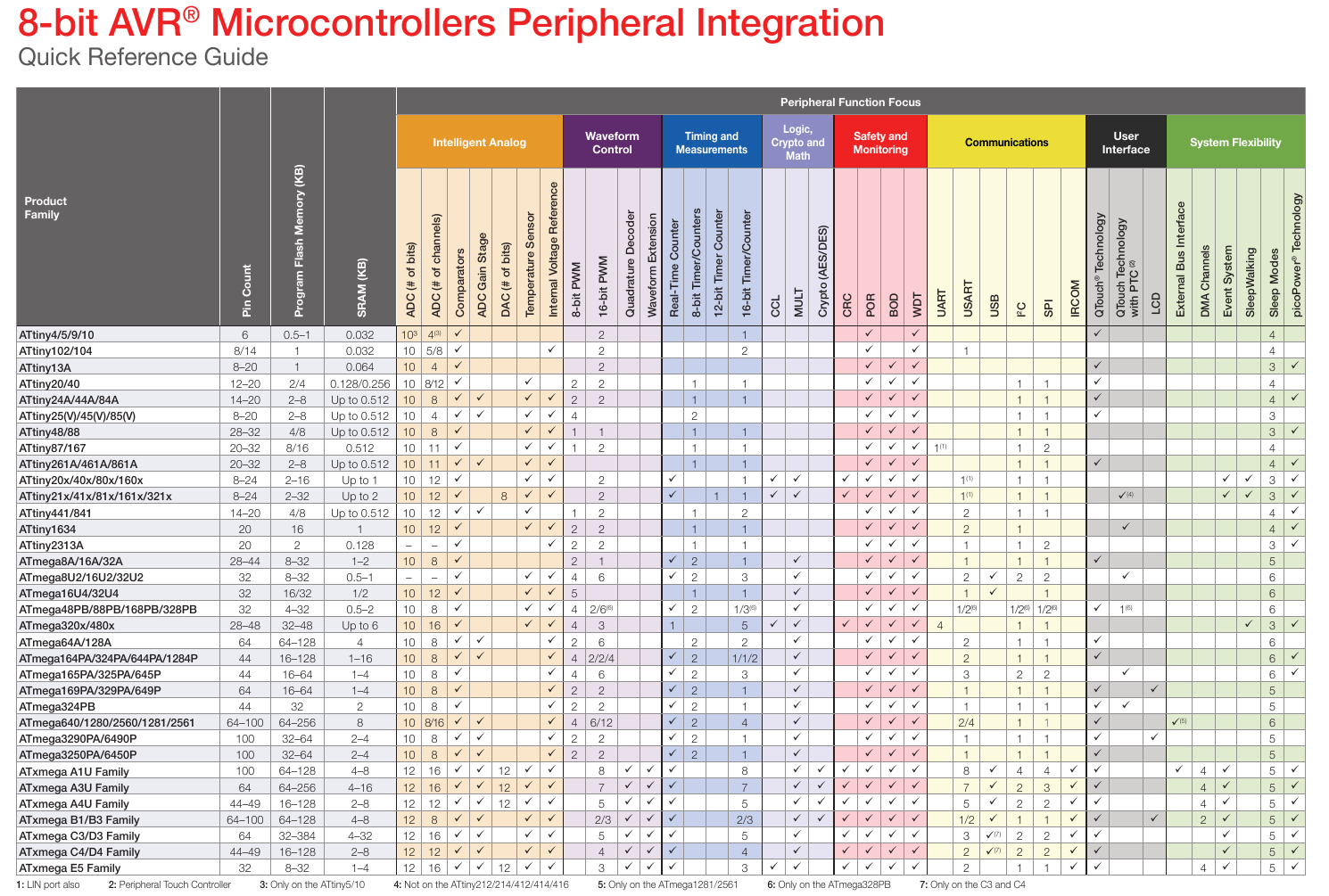

Les microC 8 bits de la famille AVR¶

Le microcontrôleur de l'Arduino UNO¶

Caractéristiques générales de l'Atmega328p¶

- Nombre de broches : 28 (sur le modèle utilisé en TP)

- Mémoire Flash : 32 ko (programmable par interface série)

- Mémoire Données EEPROM : 1 ko

- Mémoire RAM : 2 ko

- 32 registres de travail d'accès rapide pour l'ALU

- Ports parallèles : 3, avec 23 broches E/S

- Fréquence d'horloge : 16 Mhz (maxi tolérée = 20 Mhz)

- donc : 16 cycles d'horloge par micro-seconde

- Périphériques internes

- 6 convertisseur Analogique/Numérique 10 bits, comparateur analogique

- 1 timer 16 bits (T1), 2 timers 8 bits(T0,T2)

- 6 canaux PWM, 1 chien de garde (watchdog)

- SPI, USART, TWI (=I2C)

- 26 interruptions

- 5 modes d'économie d'énergie

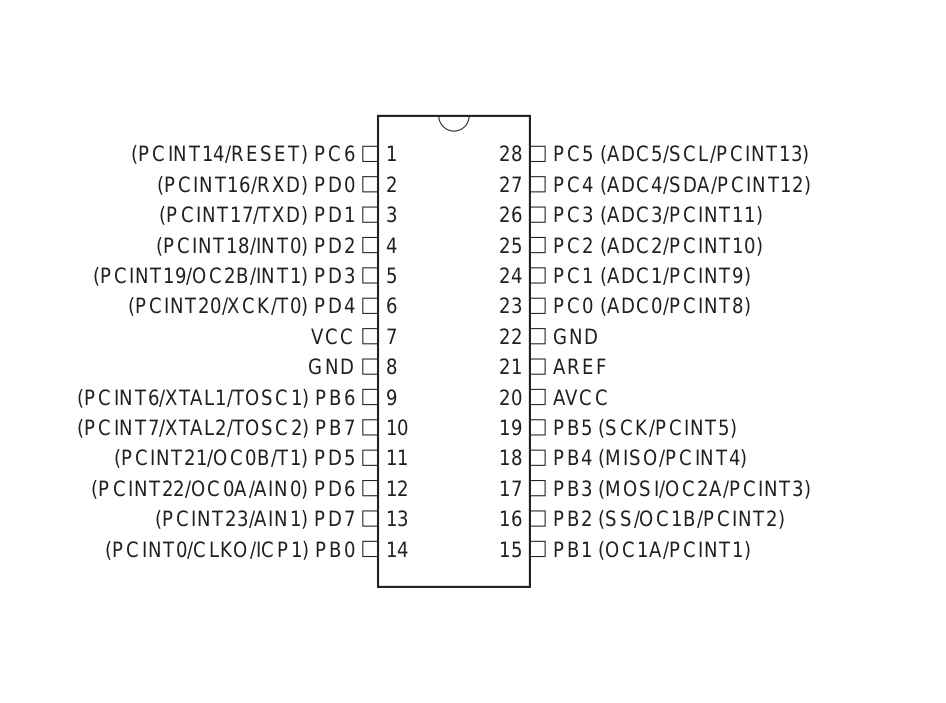

Brochage de l'ATmega 328p¶

- VCC (1), GND (2)

- E/S (=GPIO) : PORTB (8), PORTC (7), PORTD(8)

- AVCC (1) : alimentation CAN

- AREF (1) : entrée comparateur analogique

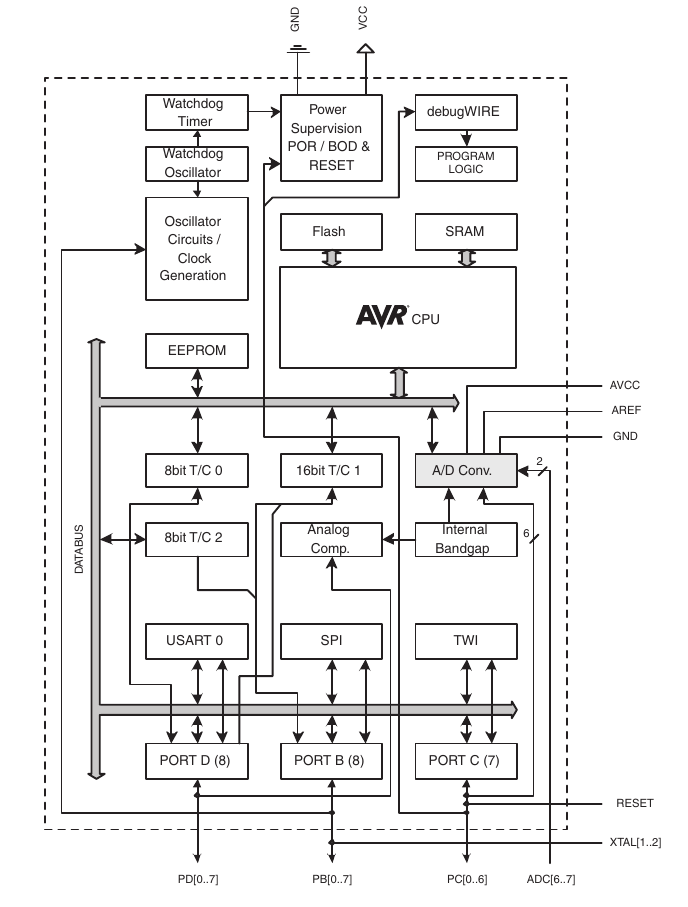

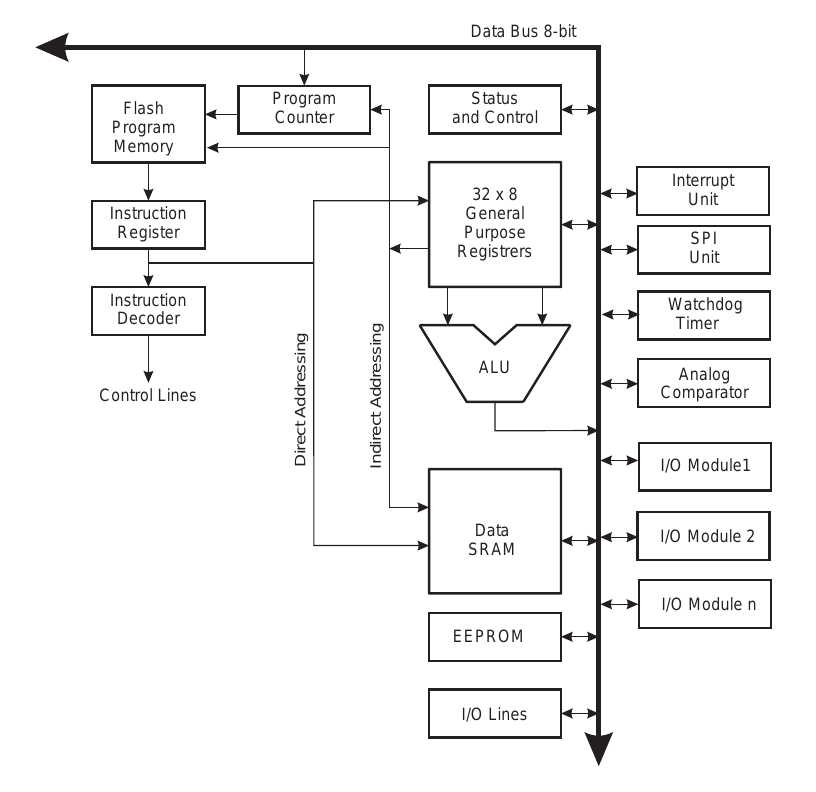

Architecture interne générale de l'ATmega 328¶

Architecture interne de l'unité centrale de l'ATmega 328¶

Schéma¶

Une architecture performante¶

-

Architecture Harvard : 3 accès mémoires indépendants

- Mémoire Programme (Flash)

- liée directement à l'ALU et au bloc de 32 registres de travail internes

- propre bus de données

- Autres mémoires + autres ressources

- partagent un même bus de données

- Mémoire Programme (Flash)

-

Le processeur dispose d'un pipeline à 1 niveau

- l'instruction N s'exécute,

- pendant que l'instruction N+1 est récupérée en mémoire

-

Donc : exécution d'1 instruction en 1 cycle d'horloge

- lecture de 2 opérandes dans les registres de travail

- exécution du calcul

- stockage du résultat dans les registres de travail

Organisation de la mémoire¶

¶

¶

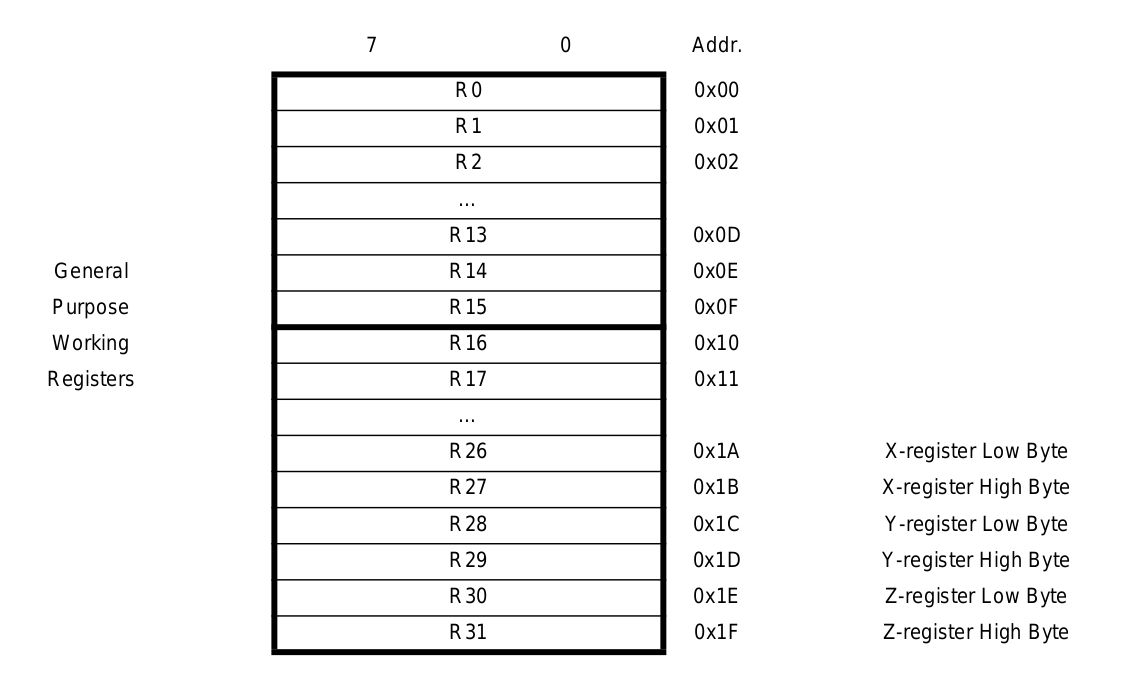

Quelques registres essentiels de l'ATmega328¶

Les registres de travail¶

- 32 registres 8 bits, R0 à R31

- certains sont utilisables en 16 bits (pour les adressages indirects)

- placés en début de la RAM de donnée

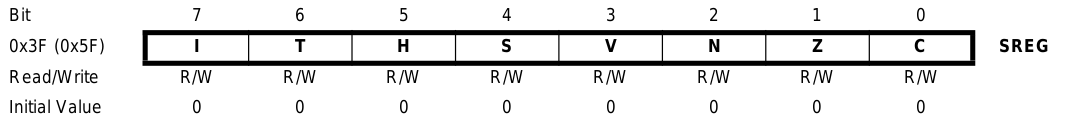

Le registre d'état SREG¶

Constitués de 8 bits, ayant chacun un rôle propre :

- I : autorisation globale des interruptions

- T : bit source ou destinataire pour les instructions de copie de bit seul

- H : demi-retenue (Half-carry) - c.-à-d. du premier quartet - sur opérations arithmétiques

- S : bit de signe

- V : bit de débordement (oVerflow)

- N : bit de résultat négatif

- Z : bit de zéro, positionné à 1 lorsque le résultat de certaines opération est nul

- C : bit de retenue (Carry)

Attention

Ce registre n'est pas sauvegardé sur la pile sur interruption ou appel de fonction.

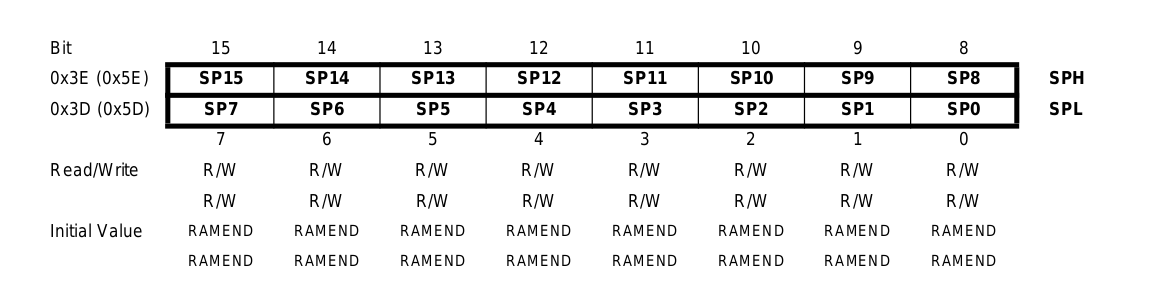

La pile et son registre « pointeur de pile »¶

- La pile est une portion de la SRAM, localisée par un registre de pointeur de pile

- Elle est manipulable via les instructions PUSH et POP

- Elle sert en particulier à sauvegarder le compteur ordinal PC (Program Counter), qui désigne l'adresse de l'instruction à exécuter

- lors d'un appel de sous-programme

- ou lors d'une interruption

- Sa position en mémoire est définie par le registre « pointeur de pile » :

¶

¶

Les interruptions de l'ATmega328¶

Définition¶

Définition : interruption

Une interruption est un déroutage automatique et « quasi-instantané » du programme en cours d'exécution, en réponse à un signal émis par un périphérique interne ou par une entrée externe (appelés sources d’interruption), vers un sous-programme permettant de gérer l’évènement.

- Le mécanisme d’interruption s’oppose à la « scrutation », où le μP interroge régulièrement l’état de la source, par logiciel

- dans la scrutation, le processeur obéit à des instructions du programme pour vérifier l'état des sources

- alors que l'interruption est déclenchée automatiquement sur demande d'une source d'interruption, indépendamment du programme en cours d'exécution

- Exemple du reset

Autorisations, priorités et mécanisme de demande d'interruption¶

- Les interruptions sont désactivables

- globalement

- ou individuellement, par source d'interruption

- La prise en compte de l’interruption peut être retardée si son niveau de priorité est insuffisant

- les niveaux de priorités sont fixes, et fonctions de la source d'interruption

- exemple : reset = interruption de plus forte priorité

-

Les sources d'interruptions (périphériques internes, entrées externes) font leur demande d'interruption en positionnant à 1 un bit dédié (interrupt flag), stocké dans l'un de leurs registres

- ainsi, une demande d'interruption non traitée faute de priorité suffisante ou faute d'autorisation, n'est pas oubliée pour autant : le drapeau reste levé

-

Sur l'ATmega328, il faut de 4 à 6 cycles d'horloge avant que le microcontrôleur exécute la routine d'interruption

Déroulement des interruptions¶

-

Sur une interruption, voici ce qui se produit

- l'instruction en cours s'achève

- le masque d'interruption I est automatiquement mis à 1 pour empêcher d'autres interruptions

- le compteur ordinal PC est sauvegardé sur la pile (au contraire de SREG)

- PC est ensuite chargé avec le vecteur d'interruption (qui effectue normalement un saut vers le sous-programme d'interruption)

-

En fin d'exécution de la routine d'interruption, c'est l'inverse

- PC est chargé avec le dessus de la pile

- I est remis à 0

- le programme reprend alors là où il avait été interrompu

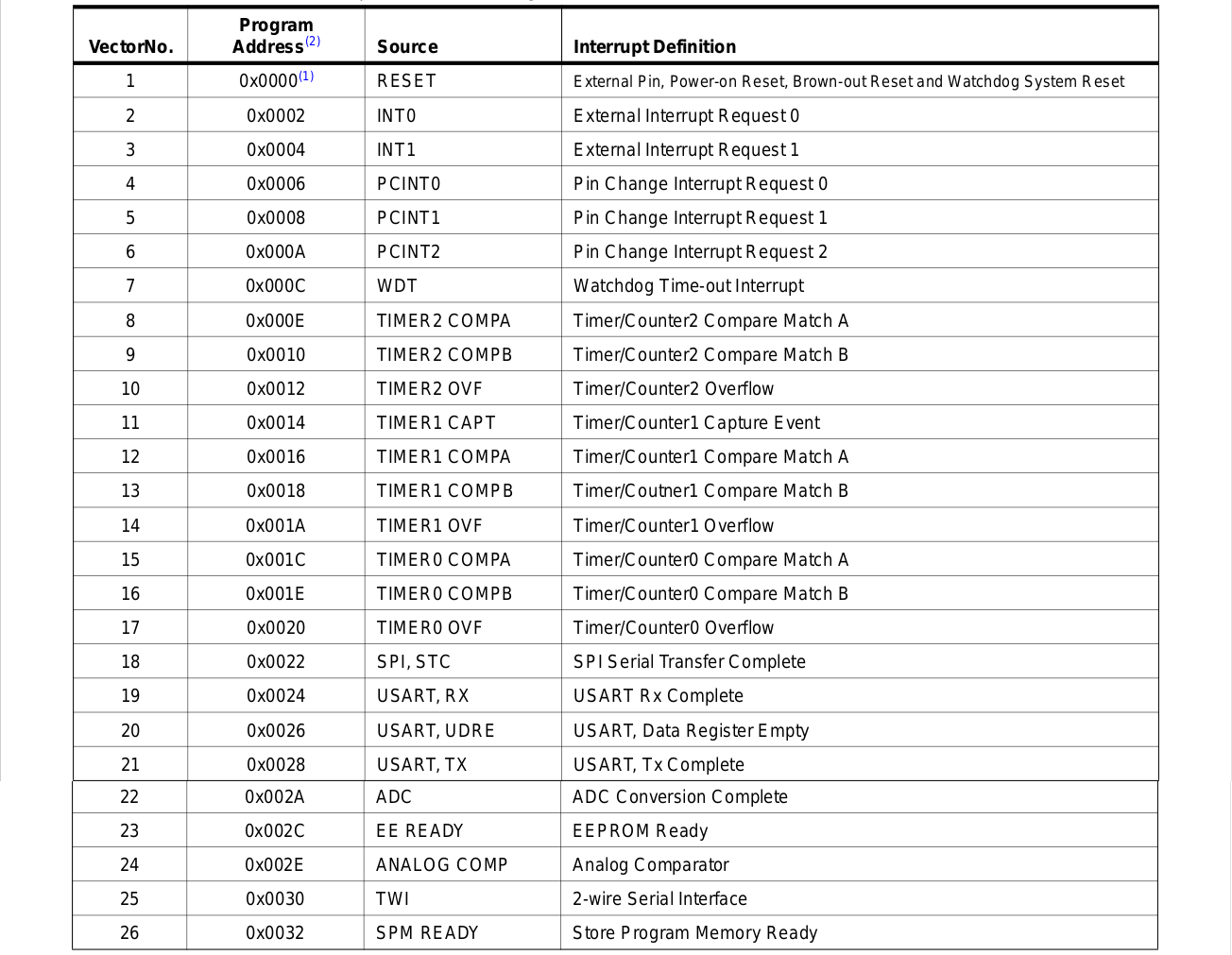

Liste des interruptions de l'ATmega328¶

- 26 sources d'interruptions

- leurs vecteurs sont constitués de 2 mots d'instructions

- ils sont ordonnés par priorité décroissante

- vecteur 0 = *reset : le plus prioritaire